# FC51L04SFSA (2A)

Operation Temperature Condition -40°C~85°C

# eMMC Flash

# 3.3V 4 Gbyte eMMC Flash Memory

### Features

- Compatible to JEDEC Embedded Multi Media Card (eMMC) Electrical Standard (5.1)

- Data bus width: 1bit (default), 4bit and 8bit

- Not support large sector size (4KB)

- Interface power: V<sub>CCQ</sub> (1.70V~1.95V or 2.7V~3.6V), Memory power: V<sub>CC</sub> (2.7V~3.6V)

- Temperature: Operation (-40°C~85°C), storage (-40°C~85°C)

- User Density:

| Density | LBA (Hex) | LBA (Dec) | Capacity (Bytes) |

|---------|-----------|-----------|------------------|

| 4 GB    | 0x73A000  | 7,577,600 | 3,879,731,200    |

### **System Performance**

#### **Read/Write Performance**

| Pre                                                                | oduct ID                      | Read Sequential (MB/S)         | Write Sequential (MB/S) |  |

|--------------------------------------------------------------------|-------------------------------|--------------------------------|-------------------------|--|

| FC                                                                 | 51L04SFSA-2.5BWGI2A           | 215                            | 55                      |  |

| Note                                                               | ):                            |                                |                         |  |

| 1.                                                                 | Values given for an 8-bit bus | width, running HS400 mode from | n ESMT proprietary tool |  |

| 2. Performance numbers might be subject to changes without notice. |                               |                                |                         |  |

### Capacity according to partition

| Capactity | Boot Partition 1 | Boot Partition 2 | RPMB    |

|-----------|------------------|------------------|---------|

| 4 GB      | 4096 KB          | 4096 KB          | 4096 KB |

### **Ordering Information**

| Product ID            | Speed   | Package      | Comments |

|-----------------------|---------|--------------|----------|

| FC51L04SFSA-2.5BWGI2A | 200 MHz | 153 ball BGA | Pb-free  |

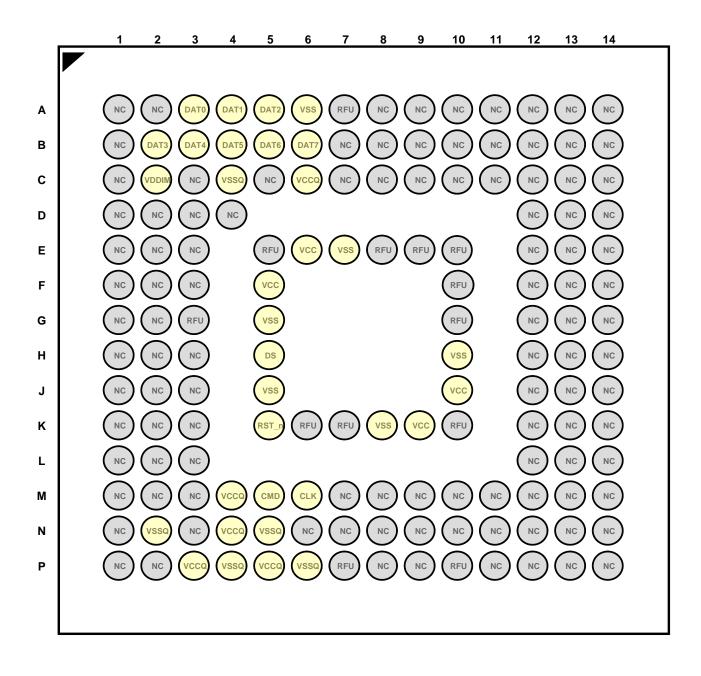

### Ball Configuration (Top View)

(BGA 153 Ball, 11.5mmx13mmx1.0mm Body, 0.5mm Ball Pitch)

### **Ball Descriptions**

| Ball Name | Type <sup>*1</sup> | Function                    |

|-----------|--------------------|-----------------------------|

| DAT0~DAT7 | I/O/PP             | Data Input/Output           |

| DS        | O/PP               | Data Strobe                 |

| CLK       | I                  | Clock                       |

| CMD       | I/O/PP/OD          | Command                     |

| VCC       | S                  | Power Supply for Flash      |

| VCCQ      | S                  | Power Supply for Controller |

| VDDIM     | -                  | Internal voltage node       |

| VSS       | S                  | Ground for Controller Flash |

| VSSQ      | S                  | I/O Ground                  |

| RST_n     | I                  | Reset                       |

| NC        | NC                 | No Connection               |

| RFU       | -                  | Reserved For Future Use     |

#### Note:

1. I: input; O: Output; PP: push-pull; OD: open-drain; NC: Not connected (or logical high); S: power supply.

# eMMC Register Value

## **OCR Register**

| OCR bit | Voltage window                   | Register Value                     |

|---------|----------------------------------|------------------------------------|

| [6:0]   | Reserved                         | 000 0000b                          |

| [7]     | 1.70 – 1.95                      | 1b                                 |

| [14:8]  | 2.0-2.6                          | 000 0000b                          |

| [23:15] | 2.7-3.6                          | 1 1111 1111b                       |

| [28:24] | Reserved                         | 000 0000b                          |

| [30:29] | Access Mode                      | 00b (byte mode), 10b (sector mode) |

| [31]    | Card power up status bit (busy)* |                                    |

**Note**\* : This bit is set to LOW if the e•MMC has not finished the power up routine. The supported voltage range is coded as shown in table.

### **CID Register**

| Name                  | Field | Width | CID-slice | CID Value     |

|-----------------------|-------|-------|-----------|---------------|

| Manufacture ID        | MID   | 8     | [127:120] | ECh           |

| Reserved              | -     | 6     | [119:114] | 0h            |

| Card/BGA              | СВХ   | 2     | [113:112] | 1h            |

| OEM/Application ID    | OID   | 8     | [111:104] | 0h            |

| Product name          | PNM   | 48    | [103:56]  | 534630303030h |

| Product revision      | PRV   | 8     | [55:48]   | 10h           |

| Product serial number | PSN   | 32    | [47:16]   | set at test   |

| Manufacture date      | MDT   | 8     | [15:8]    | set at test   |

| CRC7 checksum         | CRC   | 7     | [7:1]     | set at test   |

| not used, always '1'  | -     | 1     | [0:0]     | 1h            |

## **CSD** Register

| Name                                             | Field              | Width | Cell Type | CSD-slice | CSD Value |

|--------------------------------------------------|--------------------|-------|-----------|-----------|-----------|

| CSD Structure                                    | CSD-STRUCTURE      | 2     | R         | [127:126] | 3h        |

| System specification version                     | SPEC_VERS          | 4     | R         | [125:122] | 4h        |

| Reserved                                         | -                  | 2     | R         | [121:120] | 0h        |

| Data read access-time 1                          | TAAC               | 8     | R         | [119:112] | 2Fh       |

| Data read access-time 2 in CLK cycles (NSAC*100) | NSAC               | 8     | R         | [111:104] | 1h        |

| Max. bus clock frequency                         | TRAN_SPEED         | 8     | R         | [103:96]  | 2Ah       |

| Device command classes                           | CCC                | 12    | R         | [95:84]   | 9F5h      |

| Max. read data block length                      | READ_BL_LEN        | 4     | R         | [83:80]   | 9h        |

| Partial blocks for read allowed                  | READ_BL_PARTIAL    | 1     | R         | [79:79]   | 0h        |

| Write block misalignment                         | WRITE_BLK_MISALIGN | 1     | R         | [78:78]   | 0h        |

| Read block misalignment                          | READ_BLK_MISALIGN  | 1     | R         | [77:77]   | 0h        |

| DSR implemented                                  | DSR_IMP            | 1     | R         | [76:76]   | 0h        |

| Reserved                                         | -                  | 2     | R         | [75:74]   | 0h        |

| Device size                                      | C_SIZE             | 12    | R         | [73:62]   | FFFh      |

| Max. read current@VDD min                        | VDD_R_CURR_MIN     | 3     | R         | [61:59]   | 6h        |

| Max. read current@VDD max                        | VDD_R_CURR_MAX     | 3     | R         | [58:56]   | 6h        |

| Max. write current@VDD min                       | VDD_W_CURR_MIN     | 3     | R         | [55:53]   | 6h        |

| Max. write current@VDD max                       | VDD_W_CURR_MAX     | 3     | R         | [52:50]   | 6h        |

| Device size multiplier                           | C_SIZE_MULT        | 3     | R         | [49:47]   | 7h        |

| Erase group size                                 | ERASE_GRP_SIZE     | 5     | R         | [46:42]   | 1Fh       |

| Erase group size multiplier                      | ERASE_GRP_MULT     | 5     | R         | [41:37]   | 1Fh       |

| Write Protect group size                         | WP_GRP_SIZE        | 5     | R         | [36:32]   | 1Fh       |

| Write protect group enable                       | WP_GRP_ENABLE      | 1     | R         | [31:31]   | 1h        |

| Manufacture default ECC                          | DEFAULT_ECC        | 2     | R         | [30:29]   | 0h        |

| Write speed factor                               | R2W_FACTOR         | 3     | R         | [28:26]   | 1h        |

| Max. write data block length                     | WRITE_BL_LEN       | 4     | R         | [25:22]   | 9h        |

| Partial blocks for write allowed                 | WRITE_BL_PARTIAL   | 1     | R         | [21:21]   | 0h        |

| Reserved                                         | -                  | 4     | R         | [20:17]   | 0h        |

| Content protection application                   | CONTENT_PROT_APP   | 1     | R         | [16:16]   | 0h        |

| File format group                                | FILE_FORMAT_GRP    | 1     | R/W       | [15:15]   | 0h        |

| Copy flag(OTP)                                   | COPY               | 1     | R/W       | [14:14]   | 0h        |

| Permanent write protection                       | PERM_WRITE_PROTECT | 1     | R/W       | [13:13]   | 0h        |

| Temporary write protection                       | TMP_WRITE_PROTECT  | 1     | R/W/E     | [12:12]   | 0h        |

| File Format                                      | FILE_FORMAT        | 2     | R/W       | [11:10]   | 0h        |

| ECC code                                         | ECC                | 2     | R/W/E     | [9:8]     | 0h        |

| CRC                                              | CRC                | 7     | R/W/E     | [7:1]     | 0h        |

| Not used, always '1'                             | -                  | 1     | -         | [0:0]     | 1h        |

Elite Semiconductor Microelectronics Technology Inc.

# Extended CSD Register

| Name                                        | Field                                             | Size | Cell Type | CSD- slice | CSD Value  |

|---------------------------------------------|---------------------------------------------------|------|-----------|------------|------------|

| Reserved                                    | -                                                 | 6    | TBD       | [511:506]  | 0h         |

| Extended Security Commands Error            | EXT_SECURITY_ERR                                  | 1    | R         | [505]      | 0h         |

| Supported Command Sets                      | S_CMD_SET                                         | 1    | R         | [504]      | 1h         |

| HPI features                                | HPI_FEATURES                                      | 1    | R         | [503]      | 3h         |

| Background operations support               | BKOPS_SUPPORT                                     | 1    | R         | [502]      | 1h         |

| Max packed read commands                    | MAX_PACKED_READS                                  | 1    | R         | [501]      | 5h         |

| Max packed write commands                   | MAX_PACKED_WRITES                                 | 1    | R         | [500]      | 3h         |

| Data Tag Support                            | DATA_TAG_SUPPORT                                  | 1    | R         | [499]      | 1h         |

| Tag Unit Size                               | TAG_UNIT_SIZE                                     | 1    | R         | [498]      | 1h         |

| Tag Resources Size                          | TAG_RES_SIZE                                      | 1    | R         | [497]      | 0h         |

| Context management capabilities             | CONTEXT_CAPABILITIES                              | 1    | R         | [496]      | 5h         |

| Large Unit size                             | LARGE_UNIT_SIZE_M1                                | 1    | R         | [495]      | 0h         |

| Extended partitions attribute support       | EXT_SUPPORT                                       | 1    | R         | [494]      | 3h         |

| Supported modes                             | SUPPORTED_MODES                                   | 1    | R         | [493]      | 1h         |

| FFU features                                | FFU_FEATURES                                      | 1    | R         | [492]      | 1h         |

| Operation codes timeout                     | OPERATION_CODE_TIMEOU                             | 1    | R         | [491]      | 17h        |

| FFU Argument                                | FFU_ARG                                           | 4    | R         | [490:487]  | 0h         |

| Barrier support                             | BARRIER_SUPPORT                                   | 1    | R         | [486]      | 0h         |

| Reserved                                    | -                                                 | 177  | TBD       | [485:309]  | 0h         |

| CMD Queuing Support                         | CMDQ_SUPPORT                                      | 1    | R         | [308]      | 1h         |

| CMD Queuing Depth                           | CMDQ_DEPTH                                        | 1    | R         | [307]      | 3h         |

| Reserved                                    | -                                                 | 1    | TBD       | [306]      | 0h         |

| Number of FW sectors correctly programmed   | NUMBER_OF_FW_SECTORS<br>_CORRECTLY_PROGRAMME<br>D | 4    | R         | [305:302]  | 0h         |

| Vendor proprietary health report            | VENDOR_PROPRIETARY_HE<br>ALTH_REPORT              | 32   | R         | [301:270]  | 0h         |

| Device life time estimation type B          | DEVICE_LIFE_TIME_EST_TY<br>P_B                    | 1    | R         | [269]      | 1h         |

| Device life time estimation type A          | DEVICE_LIFE_TIME_EST_TY<br>P_A                    | 1    | R         | [268]      | 1h         |

| Pre EOL information                         | PRE_EOL_INFO                                      | 1    | R         | [267]      | 1h         |

| Optimal read size                           | OPTIMAL_READ_SIZE                                 | 1    | R         | [266]      | 8h         |

| Optimal write size                          | OPTIMAL_WRITE_SIZE                                | 1    | R         | [265]      | 8h         |

| Optimal trim unit size                      | OPTIMAL_TRIM_UNIT_SIZE                            | 1    | R         | [264]      | 8h         |

| Device version                              | DEVICE_VERSION                                    | 2    | R         | [263:262]  | 0h         |

| Firmware version                            | FIRMWARE_VERSION                                  | 8    | R         | [261:254]  | FW Version |

| Power class for 200MHz,<br>DDR at VCC= 3.6V | PWR_CL_DDR_200_360                                | 1    | R         | [253]      | 0h         |

## **Extended CSD Register - Continued**

| Name                                                                      | Field                                  | Size | Cell Type | CSD- slice | CSD Value |

|---------------------------------------------------------------------------|----------------------------------------|------|-----------|------------|-----------|

| Cache size                                                                | CACHE_SIZE                             | 4    | R         | [252:249]  | 80h       |

| Generic CMD6 timeout                                                      | GENERIC_CMD6_TIME                      | 1    | R         | [248]      | 32h       |

| Power off notification(long) timeout                                      | POWER_OFF_LONG_TIME                    | 1    | R         | [247]      | 3Ch       |

| Background operations status                                              | BKOPS_STATUS                           | 1    | R         | [246]      | 0h        |

| Number of correctly programmed sectors                                    | CORRECTLY_PRG_SECTOR<br>S_NUM          | 4    | R         | [245:242]  | 0h        |

| 1st initialization time after<br>partitioning                             | INI_TIMEOUT_AP                         | 1    | R         | [241]      | 1Eh       |

| Cache Flushing Policy                                                     | CACHE_FLUSH_POLICY                     | 1    | R         | [240]      | 0h        |

| Power class for 52MHz, DDR at $V_{CC}$ = 3.6V                             | PWR_CL_DDR_52_360                      | 1    | R         | [239]      | 0h        |

| Power class for 52MHz, DDR at $V_{CC}$ = 1.95V                            | PWR_CL_DDR_52_195                      | 1    | R         | [238]      | 0h        |

| Power class for 200MHz at V <sub>CCQ</sub> =1.95V, V <sub>CC</sub> = 3.6V | PWR_CL_200_195                         | 1    | R         | [237]      | 0h        |

| Power class for 200MHz at $V_{CCQ}$ =1.3V, $V_{CC}$ = 3.6V                | PWR_CL_200_130                         | 1    | R         | [236]      | 0h        |

| Minimum Write Performance<br>for 8bit at 52MHz in DDR mode                | MIN_PERF_DDR_W_8_52                    | 1    | R         | [235]      | 0h        |

| Minimum Read Performance<br>for 8bit at 52MHz in DDR mode                 | MIN_PERF_DDR_R_8_52                    | 1    | R         | [234]      | 0h        |

| Reserved                                                                  | -                                      | 1    | TBD       | [233]      | 0h        |

| TRIM Multiplier                                                           | TRIM_MULT                              | 1    | R         | [232]      | 2h        |

| Secure Feature support                                                    | SEC_FEATURE_SUPPORT                    | 1    | R         | [231]      | 55h       |

| Secure Erase Multiplier                                                   | SEC_ERASE_MULT                         | 1    | R         | [230]      | 1Bh       |

| Secure TRIM Multiplier                                                    | SEC_TRIM_MULT                          | 1    | R         | [229]      | 11h       |

| Boot information                                                          | BOOT_INFO                              | 1    | R         | [228]      | 7h        |

| Reserved                                                                  | -                                      | 1    | TBD       | [227]      | 0h        |

| Boot partition size                                                       | BOOT_SIZE_MULTI                        | 1    | R         | [226]      | 20h       |

| Access size                                                               | ACC_SIZE                               | 1    | R         | [225]      | 1h        |

| High-capacity erase unit size                                             | HC_ERASE_GRP_SIZE                      | 1    | R         | [224]      | 1h        |

| High-capacity erase timeout                                               | ERASE_TIMEOUT_MULT                     | 1    | R         | [223]      | 18h       |

| Reliable write sector count                                               | REL_WR_SEC_C                           | 1    | R         | [222]      | 1h        |

| High-capacity write protect group size                                    | HC_WP_GRP_SIZE                         | 1    | R         | [221]      | 20h       |

| Sleep current (VCC)                                                       | S_C_VCC                                | 1    | R         | [220]      | 7h        |

| Sleep current (VCCQ)                                                      | S_C_VCCQ                               | 1    | R         | [219]      | 7h        |

| Production state awareness timeout                                        | PRODUCTION_STATE_AWAR<br>ENESS_TIMEOUT | 1    | R         | [218]      | 17h       |

| Sleep/awake timeout                                                       | S_A_TIMEOUT                            | 1    | R         | [217]      | 17h       |

| Sleep Notification Timout <sup>1</sup>                                    | SLEEP_NOTIFICATION_TIME                | 1    | R         | [216]      | 11h       |

# **Extended CSD Register - Continued**

| Name                                                              | Field                 | Size | Cell Type | CSD- slice | CSD Value |

|-------------------------------------------------------------------|-----------------------|------|-----------|------------|-----------|

| Sector Count                                                      | SEC_COUNT             | 4    | R         | [215:212]  | 73A000h   |

| Secure Write Protect Information                                  | SECURE_WP_INFO        | 1    | R         | [211]      | 0h        |

| Minimum Write Performance<br>for 8bit at 52MHz                    | MIN_PERF_W_8_52       | 1    | R         | [210]      | Oh        |

| Minimum Read Performance<br>for 8bit at 52MHz                     | MIN_PERF_R_8_52       | 1    | R         | [209]      | 0h        |

| Minimum Write Performance<br>for 8bit at 26MHz, for 4bit at 52MHz | MIN_PERF_W_8_26_4_52  | 1    | R         | [208]      | 0h        |

| Minimum Read Performance for<br>8bit at 26MHz, for 4bit at 52MHz  | MIN_PERF_R_8_26_4_52  | 1    | R         | [207]      | 0h        |

| Minimum Write Performance<br>for 4bit at 26MHz                    | MIN_PERF_W_4_26       | 1    | R         | [206]      | 0h        |

| Minimum Read Performance<br>for 4bit at 26MHz                     | MIN_PERF_R_4_26       | 1    | R         | [205]      | Oh        |

| Reserved                                                          | -                     | 1    | TBD       | [204]      | 0h        |

| Power class for 26MHz at 3.6V 1 R                                 | PWR_CL_26_360         | 1    | R         | [203]      | 0h        |

| Power class for 52MHz at 3.6V 1 R                                 | PWR_CL_52_360         | 1    | R         | [202]      | 0h        |

| Power class for 26MHz at 1.95V 1 R                                | PWR_CL_26_195         | 1    | R         | [201]      | 0h        |

| Power class for 52MHz at 1.95V 1 R                                | PWR_CL_52_195         | 1    | R         | [200]      | 0h        |

| Partition switching timing                                        | PARTITION_SWITCH_TIME | 1    | R         | [199]      | 5h        |

| Out-of-interrupt busy timing                                      | OUT_OF_INTERRUPT_TIME | 1    | R         | [198]      | 19h       |

| I/O Driver Strength                                               | DRIVER_STRENGTH       | 1    | R         | [197]      | 1Fh       |

| Device type                                                       | DEVICE_TYPE           | 1    | R         | [196]      | 57h       |

| Reserved                                                          | -                     | 1    | TBD       | [195]      | 0h        |

| CSD STRUCTURE                                                     | CSD_STRUCTURE         | 1    | R         | [194]      | 2h        |

| Reserved                                                          | -                     | 1    | TBD       | [193]      | 0h        |

| Extended CSD revision                                             | EXT_CSD_REV           | 1    | R         | [192]      | 8h        |

| Modes Segment                                                     | ·                     |      |           |            |           |

| Command set                                                       | CMD_SET               | 1    | R/W/E_P   | [191]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [190]      | 0h        |

| Command set revision                                              | CMD_SET_REV           |      | R         | [189]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [188]      | 0h        |

| Power class                                                       | POWER_CLASS           |      | R/W/E_P   | [187]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [186]      | 0h        |

| High-speed interface timing                                       | HS_TIMING             | 1    | R/W/E_P   | [185]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [184]      | 0h        |

| Bus width mode                                                    | BUS_WIDTH             | 1    | W/E_P     | [183]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [182]      | 0h        |

| Erased memory content                                             | ERASED_MEM_CONT       | 1    | R         | [181]      | 0h        |

| Reserved                                                          | -                     | 1    | TBD       | [180]      | 0h        |

Elite Semiconductor Microelectronics Technology Inc.

### **Extended CSD Register - Continued**

| Name                                      | Field                           | Size | Cell Type                       | CSD- slice | CSD Value |

|-------------------------------------------|---------------------------------|------|---------------------------------|------------|-----------|

| Partition configuration                   | PARTITION_CONFIG                | 1    | R/W/E &<br>R/W/E_P              | [179]      | 0h        |

| Boot config protection                    | BOOT_CONFIG_PROT                | 1    | R/W &<br>R/W/C_P                | [178]      | 0h        |

| Boot bus Conditions                       | BOOT_BUS_CONDITIONS             | 1    | R/W/E                           | [177]      | 0h        |

| Reserved                                  | -                               | 1    | TBD                             | [176]      | 0h        |

| High-density erase group definition       | ERASE_GROUP_DEF                 | 1    | R/W/E_P                         | [175]      | 0h        |

| Boot write protection status registers    | BOOT_WP_STATUS                  | 1    | R                               | [174]      | 0h        |

| Boot area write protection register       | BOOT_WP                         | 1    | R/W &<br>R/W/C_P                | [173]      | 0h        |

| Reserved                                  | -                               | 1    | TBD                             | [172]      | 0h        |

| User area write protection register       | USER_WP                         | 1    | R/W,<br>R/W/C_P<br>&<br>R/W/E_P | [171]      | 0h        |

| Reserved                                  | -                               | 1    | TBD                             | [170]      | 0h        |

| FW configuration                          | FW_CONFIG                       | 1    | R/W                             | [169]      | 0h        |

| RPMB Size                                 | RPMB_SIZE_MULT                  | 1    | R                               | [168]      | 20h       |

| Write reliability setting register        | WR_REL_SET                      | 1    | R/W                             | [167]      | 0h        |

| Write reliability parameter register      | WR_REL_PARAM                    | 1    | R                               | [166]      | 15h       |

| Start Sanitize operation                  | SANITIZE_START                  | 1    | W/E_P                           | [165]      | 0h        |

| Manually start background operations      | BKOPS_START                     | 1    | W/E_P                           | [164]      | 0h        |

| Enable background operations handshake    | BKOPS_EN                        | 1    | R/W                             | [163]      | 0h        |

| H/W reset function                        | RST_n_FUNCTION                  | 1    | R/W                             | [162]      | 0h        |

| HPI management                            | HPI_MGMT                        | 1    | R/W/E_P                         | [161]      | 0h        |

| Partitioning Support                      | PARTITIONING_SUPPORT            | 1    | R                               | [160]      | 7h        |

| Max Enhanced Area Size                    | MAX_ENH_SIZE_MULT               | 3    | R                               | [159:157]  | 73h       |

| Partitions attribute                      | PARTITIONS_ATTRIBUTE            | 1    | R/W                             | [156]      | 0h        |

| Partitioning Setting                      | PARTITION_SETTING_<br>COMPLETED | 1    | R/W                             | [155]      | 0h        |

| General Purpose Partition Size            | GP_SIZE_MULT                    | 12   | R/W                             | [154:143]  | 0h        |

| Enhanced User Data Area Size              | ENH_SIZE_MULT                   | 3    | R/W                             | [142:140]  | 0h        |

| Enhanced User Data Start Address          | ENH_START_ADDR                  | 4    | R/W                             | [139:136]  | 0h        |

| Reserved                                  | -                               | 1    | TBD                             | [135]      | 0h        |

| Bad Block Management mode                 | SEC_BAD_BLK_MGMNT               | 1    | R/W                             | [134]      | 0h        |

| Production state awareness                | PRODUCTION_STATE_AWAR<br>ENESS  | 1    | R/W/E                           | [133]      | 0h        |

| Package Case Temperature is<br>controlled | TCASE_SUPPORT                   | 1    | W/E_P                           | [132]      | 0h        |

Elite Semiconductor Microelectronics Technology Inc.

### **Extended CSD Register - Continued**

| Name                                                     | Field                                  | Size | Cell Type          | CSD- slice | CSD Value |

|----------------------------------------------------------|----------------------------------------|------|--------------------|------------|-----------|

| Periodic Wake-up                                         | PERIODIC_WAKEUP                        | 1    | R/W/E              | [131]      | 0h        |

| Program CID/CSD in DDR mode support                      | PROGRAM_CID_CSD_DDR_S<br>UPPORT        | 1    | R                  | [130]      | 1h        |

| Reserved                                                 | -                                      | 2    | TBD                | [129:128]  | 0h        |

| Vendor Specific Fields                                   | VENDOR_SPECIFIC_FIELD                  | 64   | vendor<br>specific | [127:64]   | 0h        |

| Native sector size                                       | NATIVE_SECTOR_SIZE                     | 1    | R                  | [63]       | 0h        |

| Sector size emulation                                    | USE_NATIVE_SECTOR                      | 1    | R/W                | [62]       | 0h        |

| Sector size                                              | DATA_SECTOR_SIZE                       | 1    | R                  | [61]       | 0h        |

| 1st initialization after disabling sector size emulation | INI_TIMEOUT_EMU                        | 1    | R                  | [60]       | 0h        |

| Class 6 commands control                                 | CLASS_6_CTRL                           | 1    | R/W/E_P            | [59]       | 0h        |

| Number of addressed group to be Released                 | DYNCAP_NEEDED                          | 1    | R                  | [58]       | 0h        |

| Exception events control                                 | EXCEPTION_EVENTS_CTRL                  | 2    | R/W/E_P            | [57:56]    | 0h        |

| Exception events status                                  | EXCEPTION_EVENTS_STATUS                | 2    | R                  | [55:54]    | 0h        |

| Extended Partitions Attribute                            | EXT_PARTITIONS_ATTRIBUTE               | 2    | R/W                | [53:52]    | 0h        |

| Context configuration                                    | CONTEXT_CONF                           | 15   | R/W/E_P            | [51:37]    | 0h        |

| Packed command status                                    | PACKED_COMMAND_STATUS                  | 1    | R                  | [36]       | 0h        |

| Packed command failure index                             | PACKED_FAILURE_INDEX                   | 1    | R                  | [35]       | 0h        |

| Power Off Notification                                   | POWER_OFF_NOTIFICATION                 | 1    | R/W/E_P            | [34]       | 0h        |

| Control to turn the Cache ON/OFF                         | CACHE_CTRL                             | 1    | R/W/E_P            | [33]       | 0h        |

| Flushing of the cache                                    | FLUSH_CACHE                            | 1    | W/E_P              | [32]       | 0h        |

| Reserved                                                 | -                                      | 1    | TBD                | [31]       | 0h        |

| Mode config                                              | MODE_CONFIG                            | 1    | R/W/E_P            | [30]       | 0h        |

| Mode operation codes                                     | MODE_OPERATION_CODES                   | 1    | W/E_P              | [29]       | 0h        |

| Reserved                                                 | -                                      | 2    | TBD                | [28:27]    | 0h        |

| FFU status                                               | FFU_STATUS                             | 1    | R                  | [26]       | 0h        |

| Pre loading data size                                    | PRE_LOADING_DATA_SIZE                  | 4    | R/W/E_P            | [25:22]    | 0h        |

| Max pre loading data size                                | MAX_PRE_LOADING_DATA_S<br>IZE          | 4    | R                  | [21:18]    | 3A6500h   |

| Product state awareness<br>enablement                    | PRODUCT_STATE_AWARENE<br>SS_ENABLEMENT | 1    | R/W/E &<br>R       | [17]       | 3h        |

| Secure Removal Type                                      | SECURE_REMOVAL_TYPE                    | 1    | R/W & R            | [16]       | 9h        |

| Command Queue Mode Enable                                | CMDQ_MODE_EN                           | 1    | R/W/E_P            | [15]       | 0h        |

| Reserved                                                 | -                                      | 15   | TBD                | [14:0]     | 0h        |

Note : Reserved bits should be read as "0".

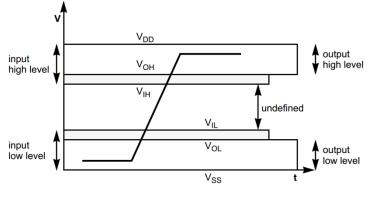

# **Bus Signal Levels**

**Bus Signal Levels**

### **Bus Signal Levels**

| Paramter                                                 | Symbol                      | Min                     | Мах                      | Unit | Remark                                          |  |  |  |  |  |  |  |  |

|----------------------------------------------------------|-----------------------------|-------------------------|--------------------------|------|-------------------------------------------------|--|--|--|--|--|--|--|--|

| Open-drain bus signal level                              | Open-drain bus signal level |                         |                          |      |                                                 |  |  |  |  |  |  |  |  |

| Output HIGH voltage                                      | V <sub>OH</sub>             | V <sub>CCQ</sub> - 0.2  | -                        | V    |                                                 |  |  |  |  |  |  |  |  |

| Output LOW voltage                                       | V <sub>OL</sub>             | -                       | 0.3                      | V    | $I_{OL} = 2mA$                                  |  |  |  |  |  |  |  |  |

| Push-pull bus signal level (2.7V~3.6V V <sub>CCQ</sub> ) |                             |                         |                          |      |                                                 |  |  |  |  |  |  |  |  |

| Output HIGH voltage                                      | V <sub>OH</sub>             | 0.75 * V <sub>CCQ</sub> | -                        | V    | I <sub>OH</sub> = -100uA @ V <sub>CCQ</sub> min |  |  |  |  |  |  |  |  |

| Output LOW voltage                                       | V <sub>OL</sub>             | -                       | 0.125 * V <sub>CCQ</sub> | V    | I <sub>OL</sub> = 100uA @ V <sub>CCQ</sub> min  |  |  |  |  |  |  |  |  |

| Input HIGH voltage                                       | VIH                         | 0.625* V <sub>CCQ</sub> | V <sub>CCQ</sub> + 0.3   | V    |                                                 |  |  |  |  |  |  |  |  |

| Input LOW voltage                                        | VIL                         | V <sub>SS</sub> - 0.3   | 0.25 * V <sub>CCQ</sub>  | V    |                                                 |  |  |  |  |  |  |  |  |

| Push-pull bus signal level (1                            | .70V~1.95V                  | Vccq)                   |                          |      |                                                 |  |  |  |  |  |  |  |  |

| Output HIGH voltage                                      | V <sub>OH</sub>             | V <sub>CCQ</sub> - 0.45 | -                        |      | I <sub>OH</sub> = - 2mA                         |  |  |  |  |  |  |  |  |

| Output LOW voltage                                       | V <sub>OL</sub>             | -                       | 0.45                     |      | $I_{OL} = 2mA$                                  |  |  |  |  |  |  |  |  |

| Input HIGH voltage                                       | VIH                         | 0.65 * V <sub>CCQ</sub> | V <sub>CCQ</sub> + 0.3   |      |                                                 |  |  |  |  |  |  |  |  |

| Input LOW voltage                                        | $VI_L$                      | V <sub>SS</sub> - 0.3   | 0.35*V <sub>CCQ</sub>    |      |                                                 |  |  |  |  |  |  |  |  |

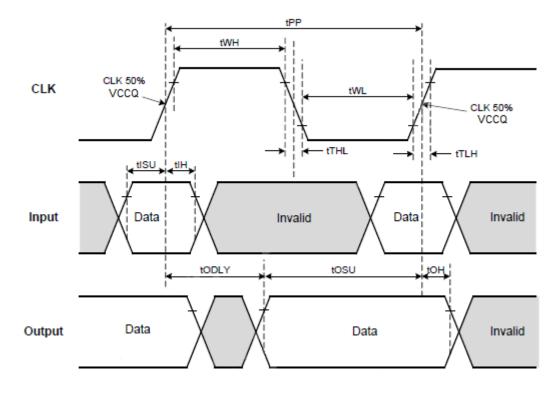

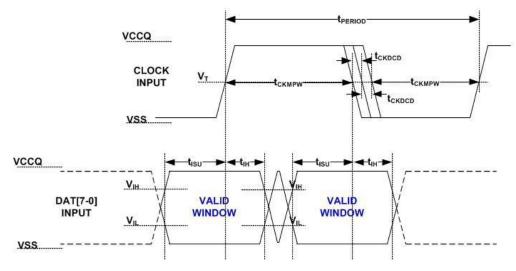

# **Bus Timing**

### **Device Interface Timings**

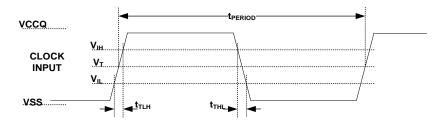

Bus Timing in Single Data Rate Mode

# FC51L04SFSA (2A)

Operation Temperature Condition -40°C~85°C

### High-Speed Device Interface Timing

| Paramter                                              | Symbol            | Min | Max              | Unit | Remark                          |

|-------------------------------------------------------|-------------------|-----|------------------|------|---------------------------------|

| Clock CLK <sup>*1</sup>                               |                   | -   |                  | •    |                                 |

| Clock frequency data transfer mode (PP) <sup>*2</sup> | f <sub>PP</sub>   | 0   | 52 <sup>*3</sup> | MHz  | CL ≤ 30pF<br>Tolerance: +100kHz |

| Clock frequency identification mode (OD)              | f <sub>OD</sub>   | 0   | 400              | kHz  | Tolerance: +20kHz               |

| Clock high time                                       | t <sub>WH</sub>   | 6.5 | -                | ns   | CL ≤ 30pF                       |

| Clock low time                                        | t <sub>WL</sub>   | 6.5 | -                | ns   | CL ≤ 30pF                       |

| Clock rise time <sup>*4</sup>                         | tтLH              | -   | 3                | ns   | CL ≤ 30pF                       |

| Clock fall time                                       | t <sub>THL</sub>  | -   | 3                | ns   | CL ≤ 30pF                       |

| Inputs CMD, DAT (referenced to CLK)                   |                   |     |                  |      | ·                               |

| Input set-up time                                     | t <sub>ISU</sub>  | 3   | -                | ns   | CL ≤ 30pF                       |

| Input hold time                                       | t <sub>IH</sub>   | 3   | -                | ns   | CL ≤ 30pF                       |

| Outputs CMD, DAT (referenced to CLK)                  |                   |     |                  |      |                                 |

| Output delay time during data transfer                | t <sub>ODLY</sub> | -   | 13.7             | ns   | CL ≤ 30pF                       |

| Output hold time                                      | t <sub>OH</sub>   | 2.5 | -                | ns   | CL ≤ 30pF                       |

| Signal rise time <sup>*5</sup>                        | t <sub>RISE</sub> | -   | 3                | ns   | CL ≤ 30pF                       |

| Signal fall time                                      | t <sub>FALL</sub> | -   | 3                | ns   | CL ≤ 30pF                       |

Note:

1. CLK timing is measured at 50% of  $V_{CCQ}$ .

2. A e•MMC shall support the full frequency range from 0 Mhz - 26 Mhz, or 0 MHz - 52 MHz

3. Device can operate as high-speed Device interface timing at 26 MHz clock frequency.

4. CLK rise and fall times are measured by min (V<sub>IH</sub>) and max (V<sub>IL</sub>).

5. Inputs CMD, DAT rise and fall times are measured by min (V<sub>IH</sub>) and max (V<sub>IL</sub>), and outputs CMD, DAT rise and fall times are measured by min (V<sub>OH</sub>) and max (V<sub>OL</sub>).

**Operation Temperature Condition -40°C~85°C**

#### **Backward Compatible Device Interface Timing**

| Paramter                                             | Symbol                               | Min  | Max | Unit | Remark <sup>*1</sup> |  |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------|------|-----|------|----------------------|--|--|--|--|--|--|

| Clock CLK <sup>*2</sup>                              |                                      |      |     |      |                      |  |  |  |  |  |  |

| Clock frequency data transfer mode $(PP)^{^{*3}}$    | f <sub>PP</sub>                      | 0    | 26  | MHz  | CL ≤ 30pF            |  |  |  |  |  |  |

| Clock frequency identification mode (OD)             | f <sub>OD</sub>                      | 0    | 400 | kHz  | -                    |  |  |  |  |  |  |

| Clock high time                                      | t <sub>WH</sub>                      | 10   | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Clock low time                                       | t <sub>WL</sub>                      | 10   | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Clock rise time <sup>*4</sup>                        | t <sub>TLH</sub>                     | -    | 10  | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Clock fall time                                      | t <sub>тнL</sub>                     | -    | 10  | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Inputs CMD, DAT (referenced to CLK)                  |                                      |      |     |      |                      |  |  |  |  |  |  |

| Input set-up time                                    | t <sub>ISU</sub>                     | 3    | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Input hold time                                      | t <sub>IH</sub>                      | 3    | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Outputs CMD, DAT (referenced to CLK)                 | Outputs CMD, DAT (referenced to CLK) |      |     |      |                      |  |  |  |  |  |  |

| Output delay time during data transfer <sup>*5</sup> | t <sub>ODLY</sub>                    | 11.7 | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

| Output hold time <sup>*5</sup>                       | t <sub>OH</sub>                      | 8.3  | -   | ns   | CL ≤ 30pF            |  |  |  |  |  |  |

#### Note:

1. The Device must always start with the backward-compatible interface timing. The timing mode can be switched to highspeed interface timing by the host sending the SWITCH command (CMD6) with the argument for high-speed interface select.

- 2. CLK timing is measured at 50% of  $V_{CCQ}$ .

- 3. For compatibility with Devices that support the v4.2 standard or earlier, host should not use > 26 MHz before switching to high-speed interface timing.

- 4. CLK rise and fall times are measured by min (V<sub>IH</sub>) and max (V<sub>IL</sub>).

5. t<sub>OSU</sub> and t<sub>OH</sub> are defined as values from clock rising edge. However, there may be Devices or devices which utilize clock falling edge to output data in backward compatibility mode. Therefore, it is recommended for hosts either to set t<sub>WL</sub> value as long as possible within the range which will not go over t<sub>CK</sub>-t<sub>OH(min)</sub> in the system or to use slow clock frequency, so that host could have data set up margin for those devices. In this case, each device which utilizes clock falling edge might show the correlation either between t<sub>WL</sub> and t<sub>OSU</sub> or between t<sub>CK</sub> and t<sub>OSU</sub> for the device in its own datasheet as a note or its' application notes.

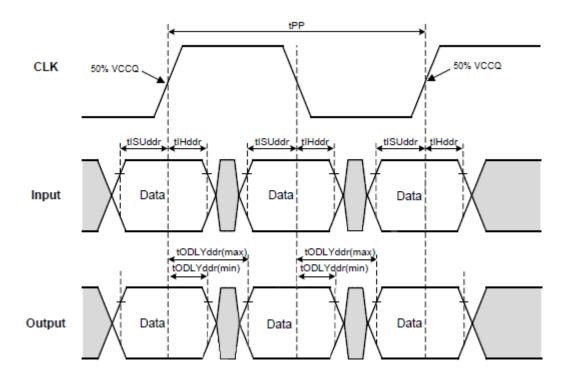

## **Dual Data Rate Interface Timings**

### Bus Timing in Dual Data Rate Mode

#### High-speed Dual Data Rate Interface Timing

| Paramter                                | Symbol               | Min | Max  | Unit | Remark                       |

|-----------------------------------------|----------------------|-----|------|------|------------------------------|

| Input CLK <sup>*1</sup>                 |                      |     |      |      | •                            |

| Clock duty cycle                        | -                    | 45  | 55   | %    | Includes jitter, phase noise |

| Clock rise time                         | t⊤∟H                 | -   | 3    | ns   | CL≤ 30pF                     |

| Clock fall time                         | t <sub>THL</sub>     | -   | 3    | ns   | CL≤ 30pF                     |

| Input CMD (referenced to CLK-SDR m      | node)                |     |      |      | ·                            |

| Input set-up time                       | t <sub>ISUddr</sub>  | 3   | -    | ns   | CL≤ 20pF                     |

| Input hold time                         | t <sub>IHddr</sub>   | 3   | -    | ns   | CL≤ 20pF                     |

| Output CMD (referenced to CLK-SDR       | mode)                |     |      | •    |                              |

| Output delay time during data transfer  | t <sub>ODLY</sub>    | -   | 13.7 | ns   | CL≤ 20pF                     |

| Output hold time                        | t <sub>OH</sub>      | 2.5 | -    | ns   | CL≤ 20pF                     |

| Signal rise time                        | t <sub>RISE</sub>    | -   | 3    | ns   | CL≤ 20pF                     |

| Signal fall time                        | t <sub>FALL</sub>    | -   | 3    | ns   | CL≤ 20pF                     |

| Input DAT (referenced to CLK-DDR m      | ode)                 |     |      | •    |                              |

| Input set-up time                       | t <sub>ISUddr</sub>  | 2.5 | -    | ns   | CL≤ 20pF                     |

| Input hold time                         | t <sub>IHddr</sub>   | 2.5 | -    | ns   | CL≤ 20pF                     |

| Output DAT (referenced to CLK-DDR       | mode)                |     |      |      |                              |

| Output delay time during data transfer  | t <sub>ODLYddr</sub> | 1.5 | 7    | ns   | CL≤ 20pF                     |

| Signal rise time (DAT0-7) <sup>*2</sup> | t <sub>RISE</sub>    | -   | 2    | ns   | CL≤ 20pF                     |

| Signal fall time (DAT0-7)               | t <sub>FALL</sub>    | -   | 2    | ns   | CL≤ 20pF                     |

Notes:

1. CLK timing is measured at 50% of  $V_{\mbox{\tiny CCQ}}.$

2. Inputs DAT rise and fall times are measured by min ( $V_{IH}$ ) and max ( $V_{IL}$ ), and outputs DAT rise and fall times are measured by min ( $V_{OH}$ ) and max ( $V_{OL}$ ).

# **Bus Timing Specification in HS200 mode**

### **HS200** Device Clock Timing

### HS200 Device Clock Timing

Note1:  $V_{IH}$  denote  $V_{IH}$ (min.) and  $V_{IL}$  denotes  $V_{IL}$ (max.).

Note2: V<sub>T</sub>=0.975V - Clock Threshold (V<sub>CCQ</sub> = 1.8V) and V<sub>T</sub>=0.65V - Clock Threshold (V<sub>CCQ</sub> = 1.2V), indicates clock reference point for timing measurements.

### **HS200 Device Clock Timing**

| Symbol     | Min. | Max.                     | Unit | Remark                                                                                                                                                      |

|------------|------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tPERIOD    | 5    | -                        | ns   | 200MHz (Max.), between rising edges                                                                                                                         |

| t⊤∟н, t⊤н∟ | -    | 0.2. t <sub>PERIOD</sub> | ns   | $t_{TLH}$ , $t_{THL}$ < 1ns (max.) at 200MHz, $C_{DEVICE}$ =6pF, The absolute maximum value of $t_{TLH}$ , $t_{THL}$ is 10ns regardless of clock frequency. |

| Duty Cycle | 30   | 70                       | %    |                                                                                                                                                             |

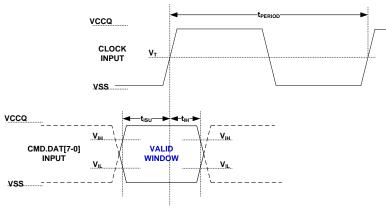

### HS200 Device Input Timing

### HS200 Device Input Timing

Note1:  $t_{\text{ISU}}$  and  $t_{\text{IH}}$  are measured at  $V_{\text{IL}}(\text{max.})$  and  $V_{\text{IH}}(\text{min.}).$

Note2:  $V_{IH}$  denote  $V_{IH}$ (min.) and  $V_{IL}$  denotes  $V_{IL}$ (max.).

### **HS200** Device Input Timing

| Symbol           | Min. | Max. | Unit | Remark                   |

|------------------|------|------|------|--------------------------|

| t <sub>ISU</sub> | 1.40 | -    | ns   | C <sub>DEVICE</sub> ≤6pF |

| t <sub>IH</sub>  | 0.8  | -    | ns   | C <sub>DEVICE</sub> ≤6pF |

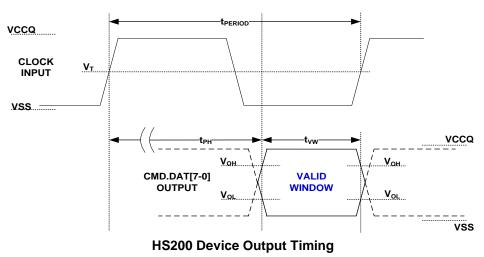

### HS200 Device Output Timing

Note:  $V_{OH}$  denotes  $V_{OH}$ (min.) and  $V_{OL}$  denotes  $V_{OL}$ (max.).

### **HS200** Device Output Timing

| Symbol          | Min.                       | Max.                      | Unit | Remark                                                                                                                                                                                                                                                                                                  |

|-----------------|----------------------------|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

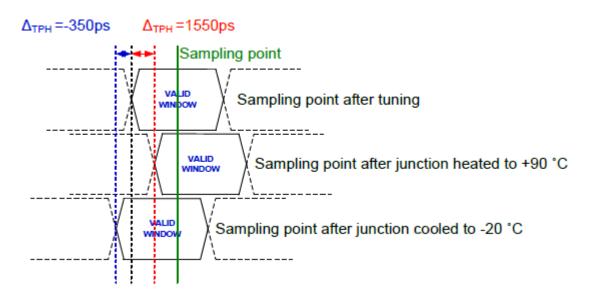

| t <sub>PH</sub> | 0                          | 2                         | UI   | Device output momentary phase from CLK input to CMD or DAT lines<br>output.<br>Does not include a long term temperature drift.                                                                                                                                                                          |

| Δтрн            | -350<br>(ΔT= -20<br>deg.C) | +1550<br>(ΔT=90<br>deg.C) | ps   | Delay variation due to temperature change after tuning.<br>Total allowable shift of output valid window (T <sub>VW</sub> ) from last system<br>Tuning procedure<br>$\Delta_{\text{TPH}}$ is 2600ps for $\Delta$ T from -25 deg.C to 125 deg.C during operation.                                         |

| t <sub>vw</sub> | 0.575                      | -                         | UI   | <ul> <li>t<sub>VW</sub>=2.88ns at 200MHz</li> <li>Using test circuit in Figure 6 including skew among CMD and DAT lines created by the Device.</li> <li>Host path may add Signal Integrity induced noise, skews, etc.</li> <li>Expected T<sub>VW</sub> at Host input is larger than 0.475UI.</li> </ul> |

Note: Unit Interval (UI) is one bit nominal time. For example, UI=5ns at 200MHz.

### $t_{\text{PH}} \text{ Consideration}$

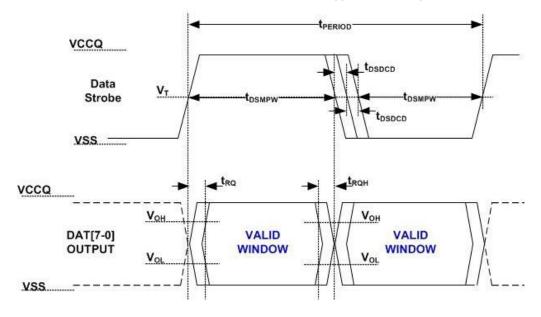

## **Bus Timing Specification in HS400 mode**

### **HS400 Device Input Timing**

The CMD input timing for HS400 mode is the same as CMD input timing for HS200 mode.

### HS400 Device Input Timing

Note:  $V_T = 50\%$  of  $V_{CCQ}$ , indicates clock reference point for timing measurements.

| Parameter                        | Symbol              | Min   | Мах | Unit | Remark                                                                                                 |  |  |  |  |  |  |  |

|----------------------------------|---------------------|-------|-----|------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Input CLK                        | Input CLK           |       |     |      |                                                                                                        |  |  |  |  |  |  |  |

| Cycle time data<br>transfer mode | tperiod             | 5     | -   | -    | 200MHz(Max), between rising edges With respect to $V_{T}$ .                                            |  |  |  |  |  |  |  |

| Slew rate                        | SR                  | 1.125 | -   | V/ns | With respect to $V_{IH}/V_{IL}$                                                                        |  |  |  |  |  |  |  |

| Duty cycle distortion            | tскосо              | 0.0   | 0.3 | ns   | Allowable deviation from an ideal 50% duty cycle. With respect to $V_T$ . Includes jitter, phase noise |  |  |  |  |  |  |  |

| Minimum pulse width              | t <sub>СКМРW</sub>  | 2.2   | -   | ns   | With respect to $V_{T}$ .                                                                              |  |  |  |  |  |  |  |

| Input DAT (referenced            | to CLK)             |       |     |      |                                                                                                        |  |  |  |  |  |  |  |

| Input set-up time                | t <sub>ISUddr</sub> | 0.4   | -   | ns   | $C_{\text{Device}} \le 6pF$<br>With respect to $V_{\text{IH}}/V_{\text{IL}}$ .                         |  |  |  |  |  |  |  |

| Input hold time                  | t <sub>IHddr</sub>  | 0.4   | -   | ns   | $C_{\text{Device}} \le 6pF$<br>With respect to $V_{\text{IH}}/V_{\text{IL}}$ .                         |  |  |  |  |  |  |  |

| Slew rate                        | SR                  | 1.125 | -   | V/ns | With respect to $V_{IH}/V_{IL}$ .                                                                      |  |  |  |  |  |  |  |

### HS400 Device Input Timing

### **HS400 Device Output Timing**

The Data Strobe is used to read data in HS400 mode. The Data Strobe is toggled only during data read or CRC status response.

### **HS400** Device Output Timing

Note:  $V_T = 50\%$  of  $V_{CCQ}$ , indicates clock reference point for timing measurements.

| Parameter                        | Symbol              | Min   | Max | Unit                | Remark                                                                                                                                                     |

|----------------------------------|---------------------|-------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Strobe                      |                     |       |     |                     |                                                                                                                                                            |

| Cycle time data<br>transfer mode | t <sub>PERIOD</sub> | 5     | -   | -                   | 200MHz(Max), between rising edges With respect to $V_T$ .                                                                                                  |

| Slew rate                        | SR                  | 1.125 | -   | V/ns                | With respect to $V_{\text{OH}}/V_{\text{OL}}$ and HS400 reference load                                                                                     |

| Duty cycle distortion            | tdsdcd              | 0.0   | 0.2 | ns                  | Allowable deviation from the input CLK duty cycle<br>distortion (t <sub>CKDCD</sub> ).<br>With respect to V <sub>T</sub> .<br>Includes jitter, phase noise |

| Minimum pulse width              | t <sub>DSMPW</sub>  | 2.0   | -   | ns                  | With respect to $V_{T}$ .                                                                                                                                  |

| Read pre-amble                   | t <sub>RPRE</sub>   | 0.4   | -   | tPERIOD             | Max value is specified by manufacturer.<br>Value up to infinite is valid                                                                                   |

| Read post-amble                  | t <sub>RPST</sub>   | 0.4   | -   | t <sub>PERIOD</sub> | Max value is specified by manufacturer.<br>Value up to infinite is valid                                                                                   |

| Output DAT (referenced           | d to Data Stro      | be)   |     |                     |                                                                                                                                                            |

| Output skew                      | t <sub>RQ</sub>     | -     | 0.4 | ns                  | With respect to $V_{\text{OH}}/V_{\text{OL}}$ and HS400 reference load                                                                                     |

| Output hold skew                 | t <sub>RQH</sub>    | -     | 0.4 | ns                  | With respect to $V_{\text{OH}}/V_{\text{OL}}$ and HS400 reference load                                                                                     |

| Slew rate                        | SR                  | 1.125 | -   | V/ns                | With respect to $V_{\text{OH}}/V_{\text{OL}}$ and HS400 reference load                                                                                     |

#### HS400 Device Output Timing

#### **Bus Signal Line Load**

| Paramter                              | Symbol              | Min | Тур | Max | Unit | Remark                 |

|---------------------------------------|---------------------|-----|-----|-----|------|------------------------|

| Pull-up resistence for CMD            | R <sub>CMD</sub>    | 4.7 | -   | 100 | KOhm |                        |

| Pull-up resistence for DAT0-DAT7      | R <sub>DAT</sub>    | 10  | -   | 100 | KOhm |                        |

| Internal pull up resistance DAT1-DAT7 | R <sub>int</sub>    | 10  | -   | 150 | KOhm |                        |

| Bus signal line capacitance           | CL                  | -   | -   | 30  | pF   |                        |

| Single Device capacitance             | C <sub>Device</sub> | -   | -   | 12  | pF   |                        |

| Maximum signal line inductance        | -                   | -   | -   | 16  | nH   | f <sub>PP</sub> ≤52MHz |

#### **HS400** Capacitance and Resistors

| Paramter                             | Symbol              | Min | Тур | Max | Unit | Remark |

|--------------------------------------|---------------------|-----|-----|-----|------|--------|

| Pull-down resistance for Data Strobe | R <sub>DS</sub>     | 10  | -   | 100 | KOhm |        |

| Single Device capacitance            | C <sub>DEVICE</sub> | -   | -   | 6   | pF   |        |

Note: Recommended maximum value is 50 KOhm for 1.8V interface supply voltages.

### eMMC DC Parameter

#### **Supply Voltage**

| Item             | Min       | Мах       | Unit |

|------------------|-----------|-----------|------|

| V <sub>CCQ</sub> | 1.70(2.7) | 1.95(3.6) | V    |

| Vcc              | 2.7       | 3.6       | V    |

| V <sub>SS</sub>  | -0.5      | 0.5       | V    |

#### **Power Consumption**

| Power Consumption                         |       | NAND | Controller | Unit |  |

|-------------------------------------------|-------|------|------------|------|--|

| $V_{CC} = 3.3V, V_{CCQ} = 1.8V$           |       |      |            |      |  |

| Active power consumption during operation | Read  | 34   | 110        | mA   |  |

|                                           | Write | 67   | 216        | mA   |  |

| Lower power mode(stand-by) <sup>(3)</sup> |       | 16.6 | 61         | uA   |  |

| Lower power mode(sleep) (4)               |       | 0    | 61         | uA   |  |

Note:

1. Test condition: Bus width x8, 200 MHz DDR, 512KB data transfer, measured on internal board, 25°C.

2. The measurement for max RMS current is the average RMS current consumption over a period of 100ms.

3. Power measurement conditions: Bus configuration = x8, No CLK.

4. Bus configuration = x8, No CLK. In sleep state, triggered by CMD5. Flash V<sub>CC</sub> power supply is switched off.

For 2.7 V - 3.6 V  $V_{\text{CCQ}}$  range (compatible with JESD8C.01)

### Push-pull signal level - high-voltage

| Paramter            | Symbol          | Min                      | Мах                      | Unit | Conditions                                       |

|---------------------|-----------------|--------------------------|--------------------------|------|--------------------------------------------------|

| Output HIGH voltage | V <sub>OH</sub> | 0.75 * V <sub>CCQ</sub>  | -                        | V    | I <sub>OH</sub> = -100 μA @ V <sub>CCQ</sub> min |

| Output LOW voltage  | V <sub>OL</sub> | -                        | 0.125 * V <sub>CCQ</sub> | V    | I <sub>OL</sub> = 100 μA @ V <sub>CCQ</sub> min  |

| Input HIGH voltage  | V <sub>IH</sub> | 0.625 * V <sub>CCQ</sub> | V <sub>CCQ</sub> + 0.3   | V    |                                                  |

| Input LOW voltage   | V <sub>IL</sub> | V <sub>SS</sub> - 0.3    | 0.25 * V <sub>CCQ</sub>  | V    |                                                  |

For 1.70V - 1.95V  $V_{CCQ}$  range

### Push-pull signal level - 1.70V-1.95V $V_{CCQ}$ voltage range

| Paramter            | Symbol          | Min                                    | Мах                                    | Unit | Conditions             |

|---------------------|-----------------|----------------------------------------|----------------------------------------|------|------------------------|

| Output HIGH voltage | V <sub>OH</sub> | V <sub>CCQ</sub> - 0.45                | -                                      | V    | I <sub>OH</sub> = -2mA |

| Output LOW voltage  | V <sub>OL</sub> | -                                      | 0.45                                   | V    | I <sub>OL</sub> = 2mA  |

| Input HIGH voltage  | VIH             | 0.65 * V <sub>CCQ</sub> <sup>(1)</sup> | V <sub>CCQ</sub> + 0.3                 | V    |                        |

| Input LOW voltage   | V <sub>IL</sub> | V <sub>SS</sub> - 0.3                  | 0.35 * V <sub>CCQ</sub> <sup>(2)</sup> | V    |                        |

Note:

1. 0.7 \*  $V_{\text{DD}}$  for MMC4.3 and older revisions.

2. 0.3 \*  $V_{\text{DD}}$  for MMC4.3 and older revisions.

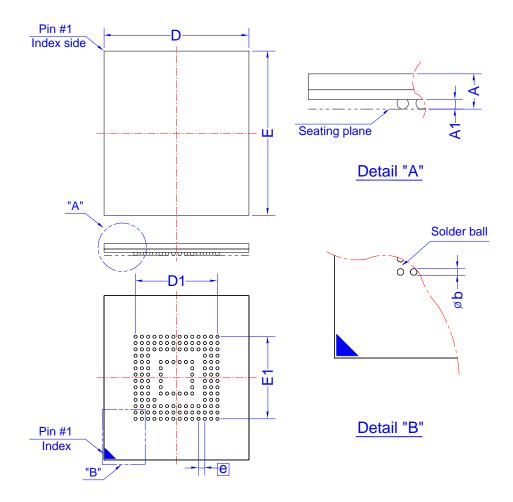

### PACKING DIMENSIONS

153-BALL (11.5x13 mm)

| Symbol                | Dimension in mm |       |       | Dimension in inch |           |       |

|-----------------------|-----------------|-------|-------|-------------------|-----------|-------|

|                       | Min             | Norm  | Max   | Min               | Norm      | Max   |

| Α                     | 0.90            | 1.00  | 1.10  | 0.035             | 0.039     | 0.043 |

| <b>A</b> <sub>1</sub> | 0.17            | 0.22  | 0.27  | 0.007             | 0.009     | 0.011 |

| Φ <sub>b</sub>        | 0.25            | 0.30  | 0.35  | 0.010             | 0.012     | 0.014 |

| D                     | 11.40           | 11.50 | 11.60 | 0.449             | 0.453     | 0.457 |

| Е                     | 12.90           | 13.00 | 13.10 | 0.508             | 0.512     | 0.516 |

| <b>D</b> <sub>1</sub> | 6.50 BSC        |       |       |                   | 0.256 BSC |       |

| E <sub>1</sub>        | 6.50 BSC        |       |       | 0.256 BSC         |           |       |

| е                     | 0.50 BSC        |       |       | 0.020 BSC         |           |       |

**Controlling dimension: Millimeter.** (Revision date: Jan 13 2020)

### **Revision History**

| Revision | Date       | Description                                  |

|----------|------------|----------------------------------------------|

| 0.1      | 2023/04/14 | Original                                     |

| 0.2      | 2023/05/18 | Modify Ext-CSD [308] and Ext-CSD [307] value |

| 0.3      | 2023/10/17 | Modify power consumption table               |

| 1.0      | 2023/11/06 | Delete Preliminary [on title]                |

# **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.